オープンソースシミュレータIcarus Verilogをインストールする

Icarus Verilogは、Verilog HDLで記述されたデジタル回路をコンパイル・シミュレーションするためのオープンソースのツールです。

Windows用パッケージをインストールし、コマンドを解説します。

Icarus Verilog とは

Icarus Verilogとはオープンソース(GPLライセンス)の論理回路シミュレータです。

Verilog HDL で記述されたデジタル回路を論理シミュレーションすることができます。

LinuxやWindowsやMacOSなどに対応しています。

主な機能を示します。

- Verilog記述のコンパイル

RTL記述(Verilog-1995、2001、2005)を実行形式に変換します。 - シミュレーション実行

vvpコマンドでシミュレーションを実行します。 - 波形出力機能

$dumpfile、$dumpvars を使用してVCDファイルを出力します。 - VPIサポート

Verilog Procedural Interface(C言語連携)も可能です。 - SystemVerilogサポート

一部の記述に対応しています。

wikipediaに解説があります。

オープンソースですが個人で開発されているものです。

SystemVerilogやUVMといった比較的新しい機能のサポートは望めないでしょう。

また大規模なSoC検証や高度なデバッグ機能も望めないでしょう。

利用用途としては個人の学習用と考えたのがよさそうです。

- 教育目的でのHDL学習

- 小規模デジタル回路の検証

- Verilogコードの検証・デバッグ

- オープンソースツールとの連携

インストール手順

バイナリパッケージをダウンロードし、インストーラを実行するだけです。

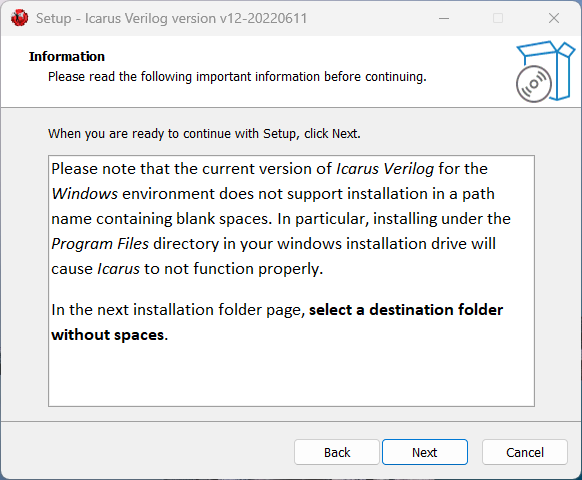

フォルダ名に空白文字が許されないことだけ注意が必要です。

こちらにWindows用のバイナリパッケージがあります。

Icarus VerilogとGTKWaveが含まれています。

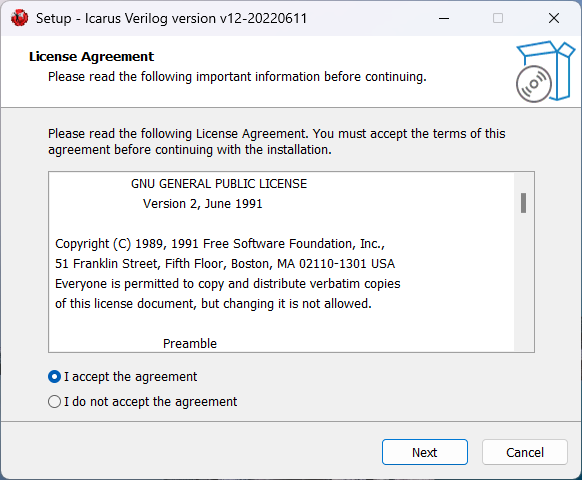

ダウンロードしたインストーラーを起動します。

”I accept the agreement”を選択します。

インストールフォルダ名に空白文字がないようにしなければならない。

と情報が表示されています。

設定は次のウィンドウで設定します。

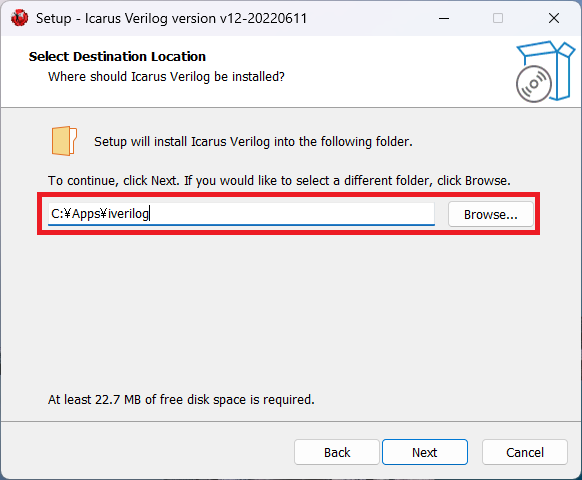

初期状態では C:\iverilog かもしれません。

私は C:\Apps\iverilog に変更しています。

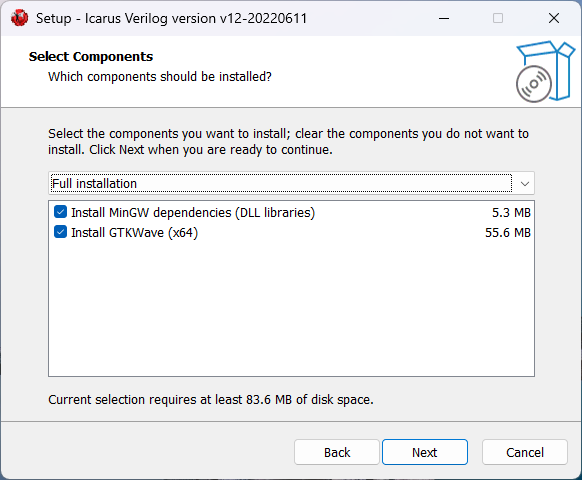

インストール不要なものがあればチェックを外します。

デフォルトのままでよいと思います。

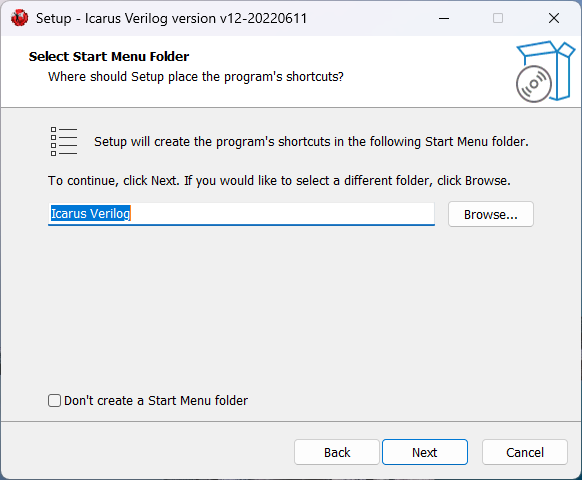

メニューフォルダ名の設定です。

デフォルトのままでよいと思います。

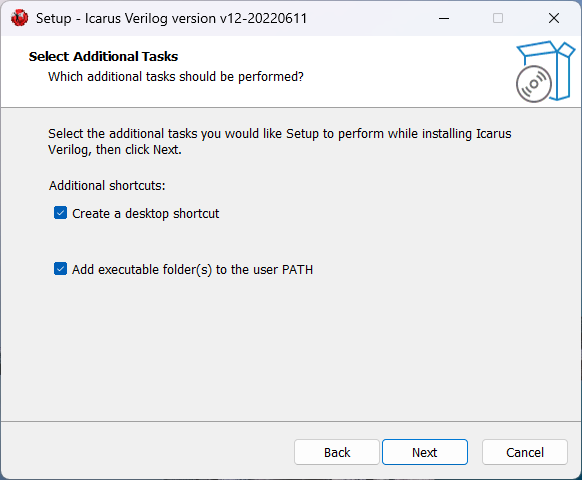

デスクトップアイコンを作るか。PATHを設定するかの指定です。

デフォルトのままでよいと思います。

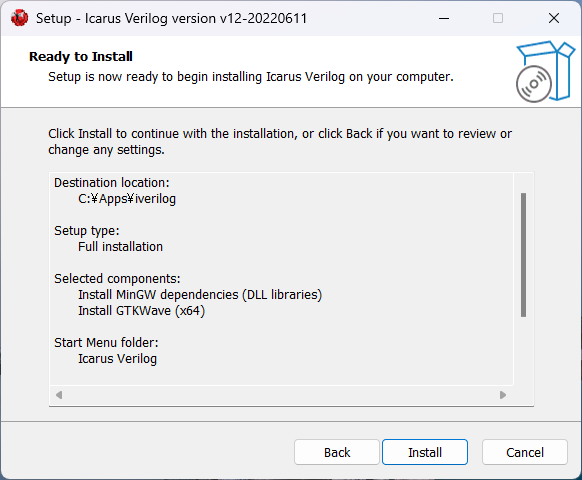

設定が完了しました。

Installを押すとインストールを開始します。

しばらくするとインストールが完了し、完了を知らせるメッセージが表示され終了です。

環境確認

フォルダメニューを見ると二つのアイコンがあります。

「Icarus Verilog」でインストールフォルダを表示します。

「Icarus Verilog on the Web」でサイトを開こうとしますが、すでに存在しないサイトです。

この2つのアイコンはあまり用途がないと思われます。

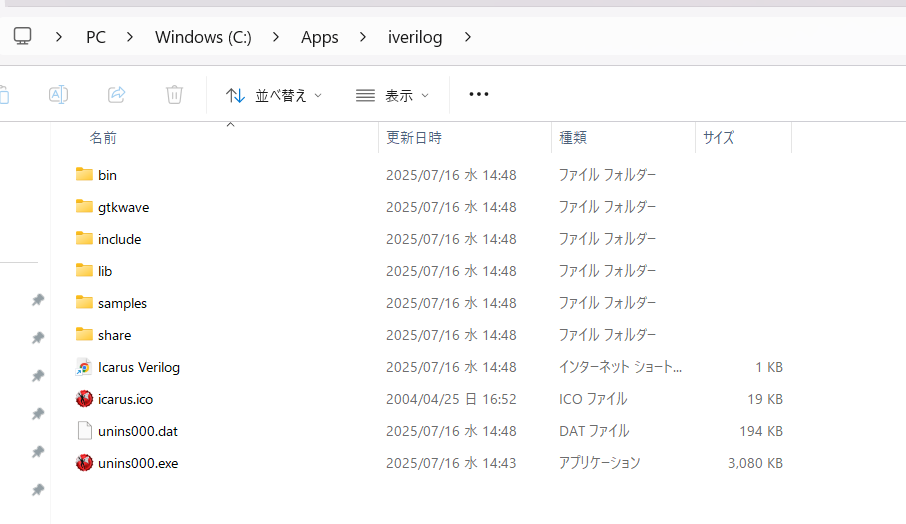

メニューの「Icarus Verilog」で以下のようにインストールフォルダを表示します。

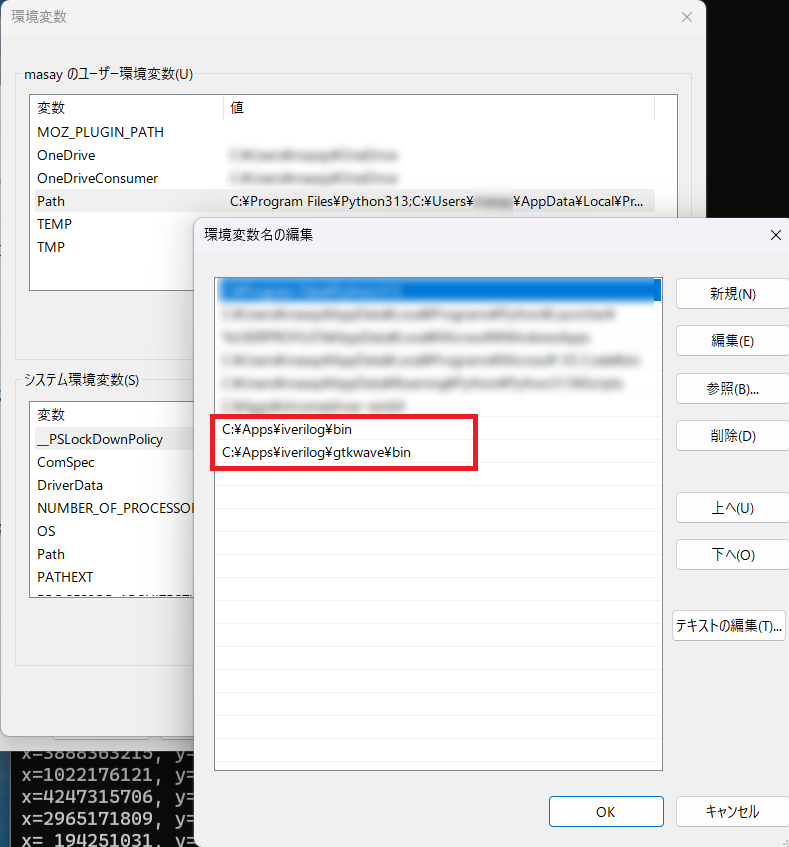

コマンドiverilogはbinにあります。

コマンドgtkwaveはgtkwave\binにあります。

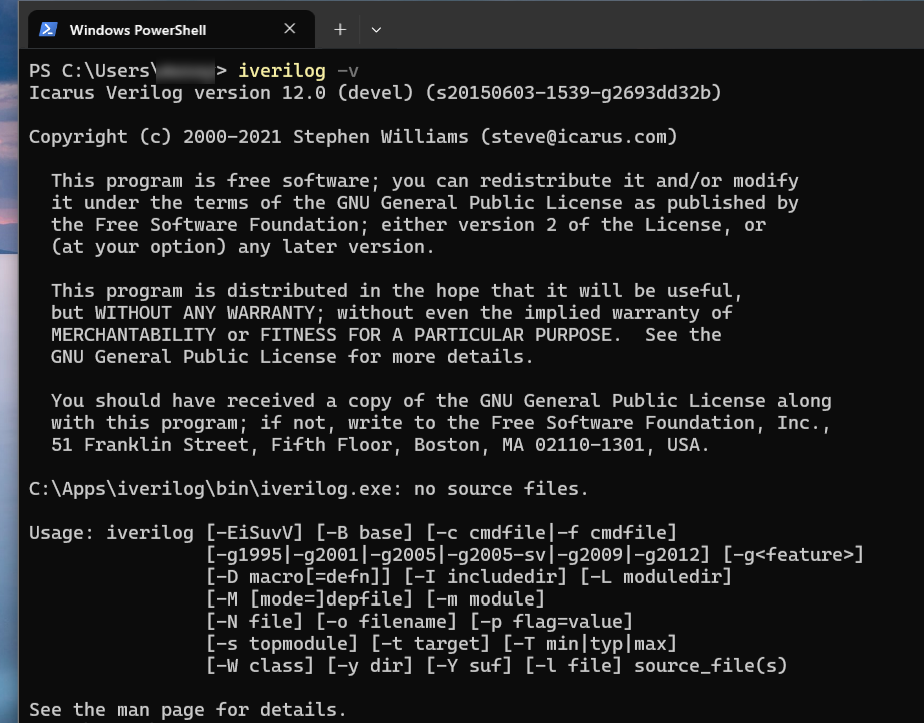

PowerShellを起動してコマンドを確認します。

インストール時にPATHは設定されているはずなので、起動するはずです。

iverilog -v で以下のようにバージョンが表示されます。

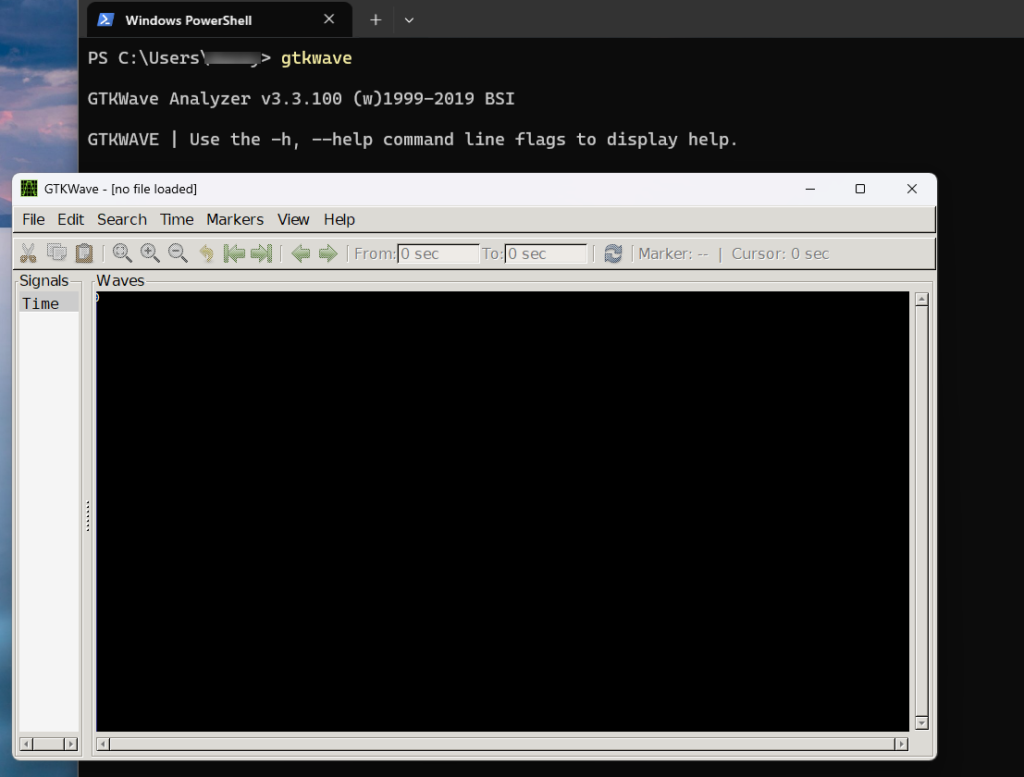

コマンドgtkwaveでGTKWaveが起動します。

コマンドが見つからない場合は環境変数のPATHを確認しましょう。

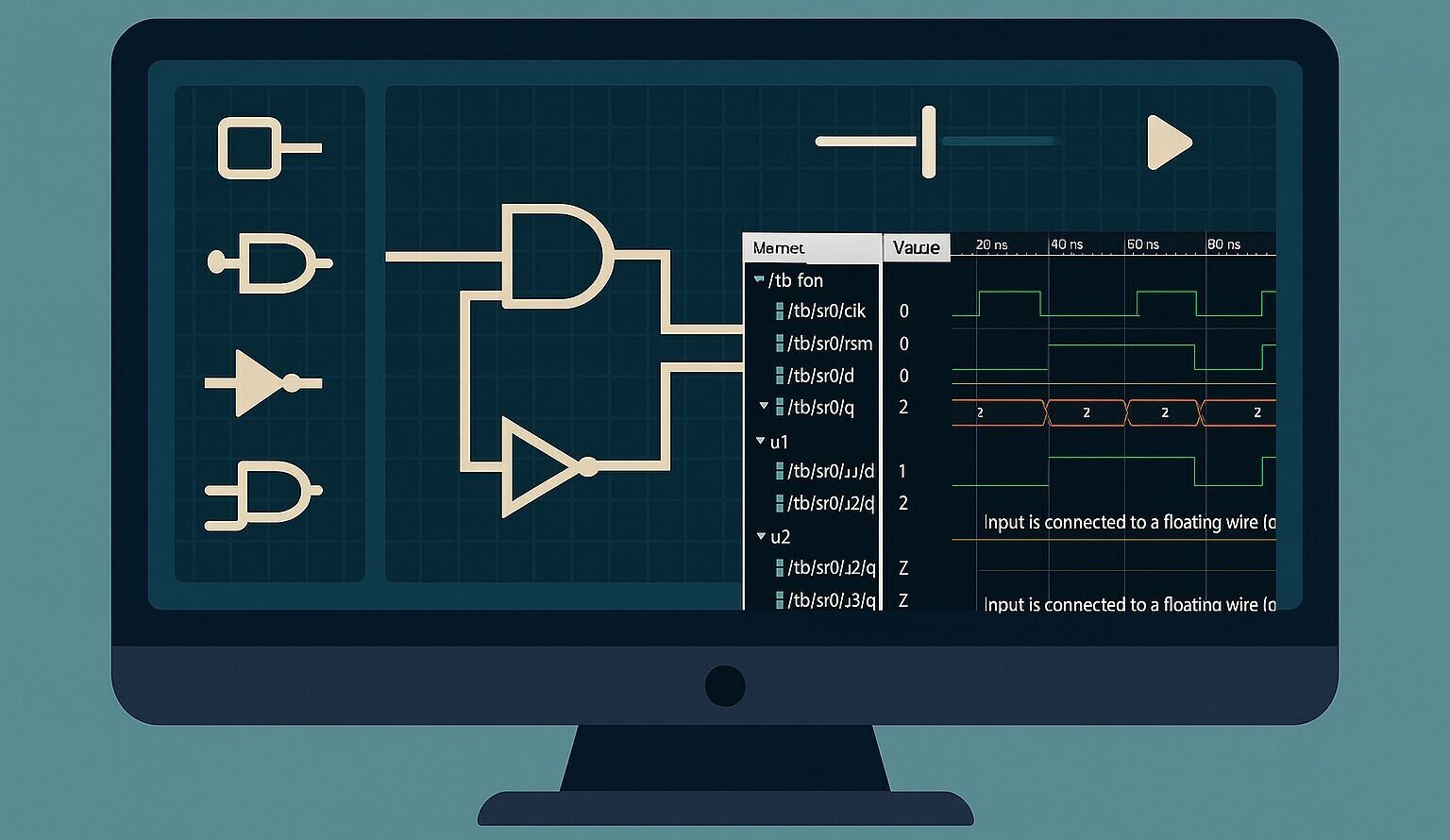

サンプルで動作確認

インストールディレクトリの下にサンプルディレクトリsamplesがあります。

ディレクトリごとコピーして動作確認してみましょう。

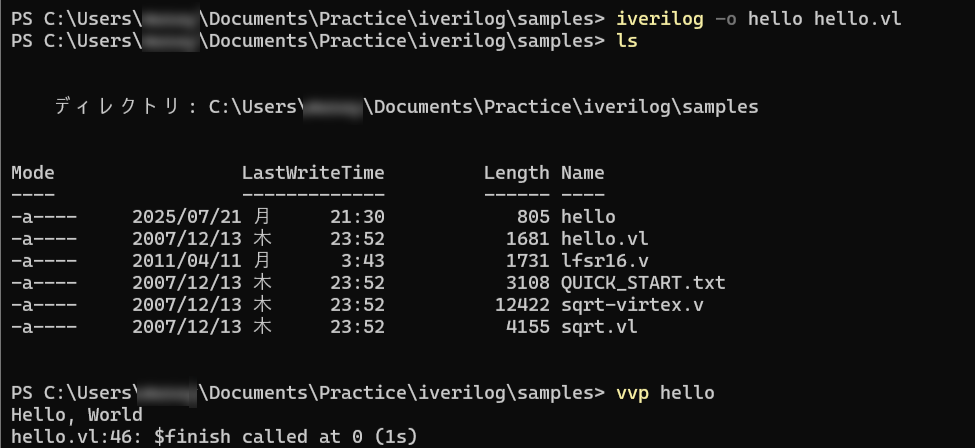

hello.vlはinitial文で$displayを実行するだけの記述です。

iverilog -o hello hello.vl でhelloを作り、vvpで実行します。

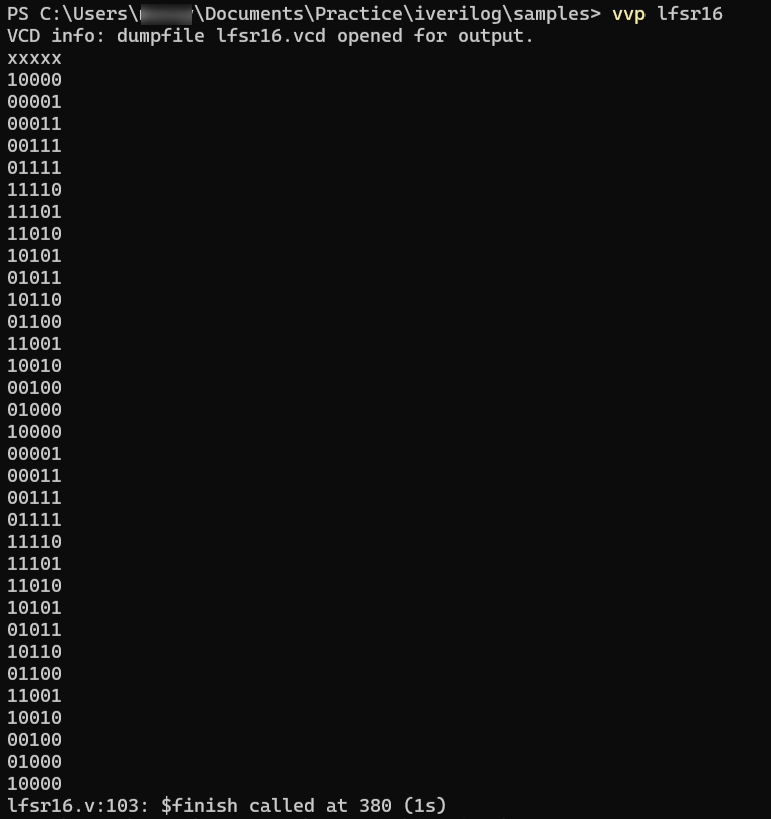

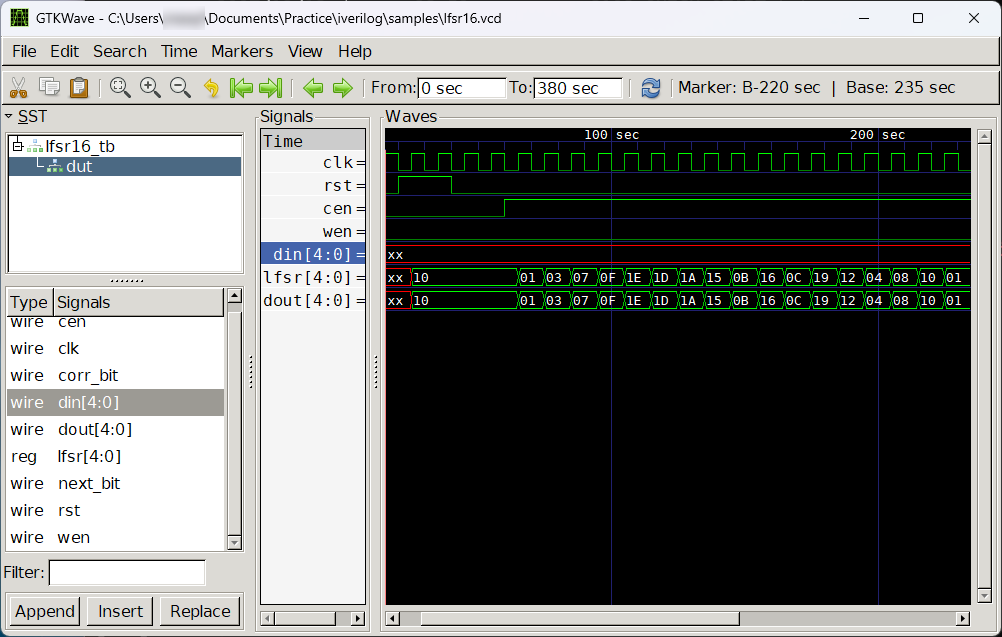

lfsr16.vは線形フィードバックシフトレジスタ(LFSR)の記述と検証環境が記述されています。

実行すると5ビットのデータをログに出力し、vcdファイルも出力します。

このLFSRは16系列のデータを繰り返し出力しています。

以下にgtkwaveでvcdファイルを表示した例を示します。

値は16進で表示されていて、ログと対応しています。

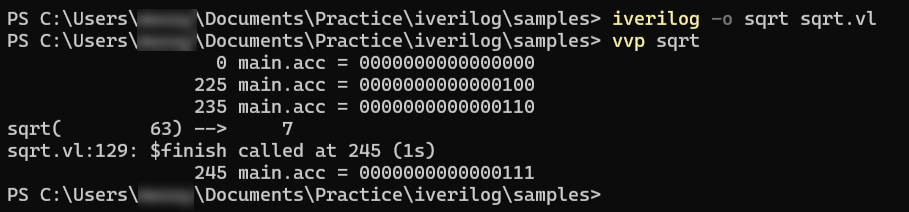

sqrt.vlは平方根を求める回路と検証環境の記述です。

テストでは63の平方根を求めています。

63の平方根は7.937…です。整数部の7が求められています。

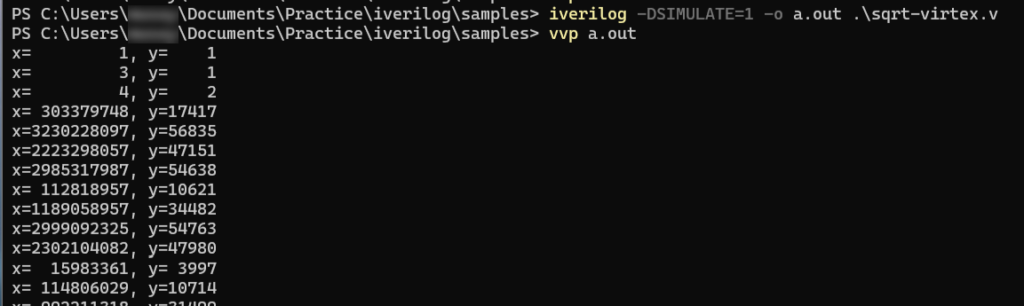

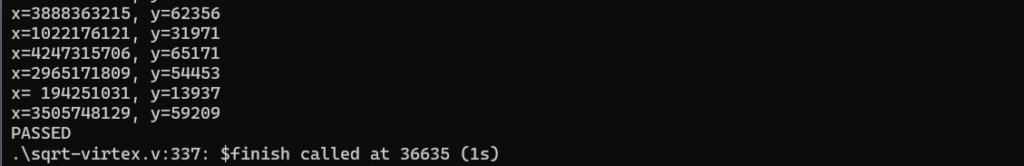

sqrt-virtex.vはFPGA(Virtex系)向けに最適化された平方根演算回路と見られます。

-DSIMULATE=1は検証環境の制御用に使われているディレクティブの指定です。

正確な動作をしているかまでは確認していませんが、ひとまず実行できていることはわかりました。

コマンド解説

インストールされたコマンドを簡単に見ておきます。

iverilog\binにはIcarus Verilogの基本コマンドがインストールされています。

| コマンド | 用途・説明 |

| iverilog.exe | Verilogコンパイラ。Verilog記述をvvpの実行形式に変換する |

| vvp.exe | vvp実行形式のシミュレーション実行コマンド |

| iverilog-vpi.exe | VPIモジュールのビルド補助ツール。 C言語で書かれたものをWindowsのDLLに変換する |

iverilog\gtkwave\binには波形ビュアーや波形変換に関するコマンドがインストールされています。

| コマンド | 用途・説明 |

| evcd2vcd.exe | EVCD(Extended VCD)形式を通常の VCD に変換するツール。 EVCD は、信号方向(input/output)を含む詳細な VCD 拡張。 |

| fst2vcd.exe | FST(Fast Signal Trace)形式を VCD に変換。 GTKWave の高速波形形式を一般的な VCD に戻す。 |

| fstminer.exe | FST ファイル内の信号・構造を調査・解析するコマンドラインツール |

| ghwdump.exe | GHW(GHDLで生成される波形)形式をテキスト形式で出力するツール。 GHDL用。 |

| gtkwave.exe | GTKWave のメイン波形ビューア。GUIツール。.vcd や .fst を表示できる。 |

| lxt2miner.exe | LXT2(古い圧縮波形形式)ファイル内の信号などを調査。 信号階層やサイズ情報などが取得可能。 |

| lxt2vcd.exe | LXT2 → VCD への変換。古い圧縮波形を通常VCD形式に展開。 |

| rtlbrowse.exe | RTL構造をGUIでブラウズするツール。 verilogのRTL階層を視覚的に探索する用途。 |

| shmidcat.exe | shm 形式(Cadence系の一部シミュレータが出力)波形ファイルを 連結するツール。 |

| twinwave.exe | GTKWave ベースのマルチパネル波形比較ツール。2つの波形を比較できるGUI。 |

| vcd2fst.exe | VCD → FST への変換。VCDを高速・軽量なFST形式に変換して GTKWaveで効率的に閲覧可能に。 |

| vcd2lxt.exe | VCD → LXT への変換(旧圧縮波形形式への変換)。 |

| vcd2lxt2.exe | VCD → LXT2(改良版LXT)への変換。 |

| vcd2vzt.exe | VCD → VZT(Zlib圧縮された波形形式)への変換。 保存サイズを小さくする目的。 |

| vermin.exe | Verilog モジュール階層などの解析を行う静的コード解析ツール。 構造の可視化などに使用。 |

| vzt2vcd.exe | VZT → VCD への展開。 |

| vztminer.exe | VZT ファイルの構造・信号名などを解析して表示する。 |

| xml2stems.exe | XMLファイルから GTKWave の階層表示用の *.stemsファイルを 生成する補助ツール。 |

これらを把握しておく必要はありません。

しかし実際の業務では以下のようなことが考えられます。

- 特定の波形フォーマットからVCDや電力測定用フォーマットに変換する。

- ふたつの波形を比較して同じ動きをしているか、否かを判断する。

商用シミュレータを使うときも同じようにコマンド群を確認しておくと、便利なコマンドを見つけることができるかもしれません。

まとめと課題

Icarus Verilogは、軽量かつ無料で始められるVerilog HDLの開発・検証ツールです。

特に学習者や小規模開発に適しており、LinuxやWSL環境でも扱いやすいという利点があります。

今回Windows版バイナリをインストールしたことで、簡単にセットアップがすみました。

課題ですが解決しておきたいことが何点か残っています。

これらについては試行しながら解決する予定です。

- コマンドライン操作なので、MinGWなどのGNUツールチェーンがないと不便。

- WSL版をコンパイルしてインストールしたほうがよいか?

リンク

GitHub steveicarus/iverilog

GitHubにある作者のIcarus Verilogのリポジトリ

SOURCEFORGEのIcarus Verilogページ

Tarで固められたソースコードの配布元

Icarus Verilog for Windows

Windows用のバイナリパッケージの配布元。Icarus VerilogとGTKWaveが含まれる。

GTKWave

GTKWaveのページ

GitHub gtkwave repositories

GitHubにあるGTKWaveのリポジトリ

GTKWave for Windows

Windows用GTKWaveの配布元